# **Chapter 1: DC circuit basics**

#### Overview

Electrical circuit design depends first and foremost on understanding the basic quantities used for describing electricity: Voltage, current, and power. In the simplest circuits these are related by Ohm's law. After defining and understanding these quantities, we will begin a discussion of network analysis and look at a few examples.

#### Voltage

*Voltage* (measured in volts, V) is measured between two points in a circuit. It is the amount of potential energy delivered per unit charge as a charge flows along the circuit. You measure a voltage by connecting the two terminals of a voltmeter to the two points in your circuit. You must measure the voltage while your circuit is operating. If you have a good *voltmeter*, your measured voltage will be the same as the voltage was before you connected the voltmeter. A voltage decrease in the direction of current flow represents energy flowing out of the circuit (usually into heat). Voltage sources, such as batteries and power supplies, produce voltage increases along the direction of current flow.

#### Current

*Current* (measured in amperes or amps, A, which is equivalent to Coulombs/second) is measured at a single point in a circuit. It is the rate at which charge flows along the circuit. To measure a current with a *current meter* (or *ammeter*) you must break the circuit at that point and connect each end to one of the terminals of the ammeter. Current can only flow in complete circuits. That's why a switch stops an electrical circuit – it breaks the circuit and interrupts the current flow.

#### Power

*Power* (measured in Watts, W) is the rate at which electrical energy is converted into heat or some other form of energy. Since we all know that energy is conserved, a circuit needs a *power supply* or battery, which converts another form of energy into electrical energy, in order for it to operate. The power consumed is the product of the current flowing through an element times the voltage drop across the element

$$P = IV$$

(1.1)

Where *P* is the power, *I* is the current, and *V* is the voltage.

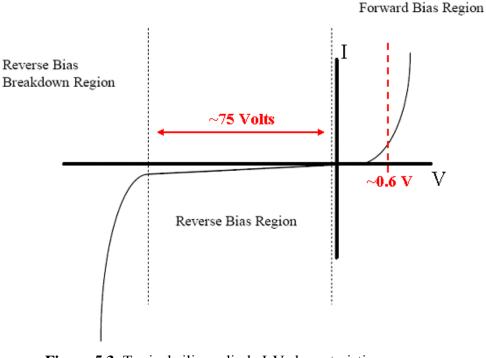

#### IV Characteristic

We can completely characterize any element that has two terminals by its "IV" characteristic (i.e. how much current flows through it when a given voltage is put across it?). The IV characteristic is given by the functions I(V) or V(I) and is frequently defined graphically.

## Ground

*Ground* is the name given to the V=0 reference point. This makes it easier to refer to voltages, since you can generally assume that the 2<sup>nd</sup> point is ground if it is not explicitly stated. We will also use it to represent the implied completion of a circuit, even when we do not explicitly show a wire connection between different places in a circuit, since all ground connections are connected together.

## Resistance

A *resistor* is a two-terminal device that converts a voltage into a current or converts a current into a voltage. The current through a resistor is always related to the voltage drop across the resistor by Ohm's Law

$$V = IR \tag{1.2}$$

where *R* is the resistance (measured in Ohms,  $\Omega$ ) This also means that a resistor generates heat when a current flows given by:

$$P = IV = I^2 R = V^2 / R.$$

(1.3)

Each of these expressions give the same answer but one or the other will be easier to use, depending on what you know about the circuit (I or V, or both).

It may seem silly to have a device that just turns electrical energy into heat, but resistors actually perform many important roles:

1. They turn electrical energy into heat. This can be useful if you want to make an electrical heater, or (more likely) a light bulb. Light is just a form of heat given off by a very hot source. Sometimes you must dissipate power somewhere. For example, if you want to deliver 100 mA current at 12 Volts to part of your circuit, but your power supply only gives you 15 Volts, then the extra power

300 mW = (100 mA) (15 V - 12 V)

must go somewhere. You dissipate it in a resistor rather than by heating your sensitive transistors.

- 2. If you have a voltage source and you want a specific amount of current then a resistor does the job. It converts a voltage difference between two points into a current flowing through the resistor. Sometimes, you will add a resistor in series in a circuit to prevent the power supply from delivering too much current in case you short the output lines together. This is called a *current limiting resistor*.

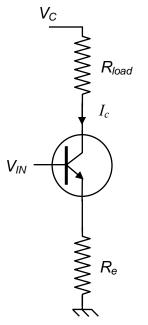

- 3. If you have a current flowing and you want to convert it into a voltage then a resistor is again the solution. This might seem a little more far-fetched, because you may not be familiar with constant *current sources*. When we begin studying transistors we will find that they will behave as current sources. So we will use a resistor on the output to convert the current into a voltage.

When we consider capacitors, in week three, we will generalize resistance for AC circuits by allowing for phase shifts. We will call this generalization to the complex plane *impedance*. For this week we will assume resistance and impedance to mean the same thing.

#### **Network Analysis**

If you connect one power supply and lots of resistors together in a complicated network, then currents will flow through all the various elements so as to insure that charge is conserved, energy is conserved, and Ohm's Law is satisfied. Simultaneously satisfying all these conditions will give you exactly one solution. We will start with two resistors and then proceed to more complicated systems. Specifically, two resistors in series will draw the same current as an equivalent resistor with resistance. This is stated mathematically as:

$$R_S = R_I + R_2 \tag{1.4}$$

Alternatively, two resistors in parallel will draw current equivalent a resistor with resistance

$$\frac{1}{R_{1/2}} = \frac{1}{R_1} + \frac{1}{R_2} \text{ or } R_{1/2} = \frac{R_1 R_2}{R_1 + R_2}$$

(1.5)

Note that the resistance of 2 resistors in parallel is always less than the smaller, but not less than half of that smaller resistance. If the two resistors differ by a large factor, then you can ignore the larger resistor. For example, a 1 k $\Omega$  in parallel with 1 M $\Omega$  is within 999  $\Omega$  or very close to 1 k $\Omega$ .

Standard resistors come in a few dozen difference ratings (more on this in lab). So in general one can get any particular value one wants. One can make up an equivalent resistor using a few resistors in series and parallel combinations to get a much larger range of options. In Design Exercise 1-1, we have you design a network to have a specific net resistance given a very limited set of resistances.

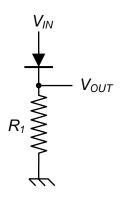

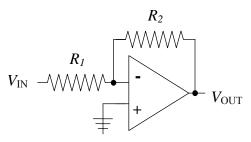

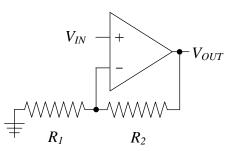

#### Voltage Dividers

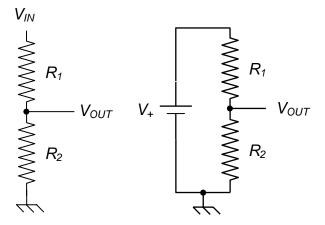

By far, the most useful thing you can do with two resistors is to make a *voltage divider*, which is just two resistors in series. Voltage dividers are shown schematically in figure 1 on the right in two slightly different but equivalent representations. It "divides" a total voltage into two parts with each part proportional to the resistance in that leg. So, if you know the starting voltage and the target voltage, then you can calculate the required ratio of the two resistors.

$$V_{OUT} = V_{IN} \left( \frac{R_2}{R_1 + R_2} \right)$$

(1.6)

**Figure 1.1**: Two alternative schematics for a same voltage divider circuit.

In Design Exercise 1-2 you get to derive this relationship.

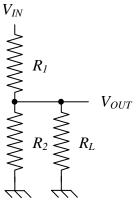

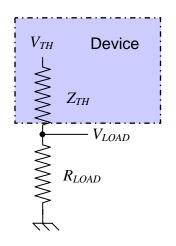

#### A Loaded Voltage Divider

Of course, the way you will use  $V_{OUT}$  from a voltage divider is to connect it to something, usually another resistor, as shown in figure 2 on the right. This then changes the equivalent resistance in the lower leg, and therefore changes the voltage across that leg!

In order to choose the actual resistor values, you have two competing concerns: (1) low resistance makes the divider less sensitive to loading when you use the target voltage (i.e. "stiffer"); and (2) high resistance draws less current, and therefore uses less power. We'll spend more time on this and formalize the considerations in the coming weeks.

For now, let's just consider what happens to our voltage divider when we connect a load resistance  $(R_L)$  from its output to ground. In this case we can replace the  $R_2$  from the

**Figure 1.2:** A loaded voltage divider.

expression for the unloaded divider with an equivalent resistance of  $R_2$  and  $R_L$  in parallel. This gives us a voltage across  $R_L$  of:

$$V_{OUT,LOADED} = V_{IN} \frac{R_{2//L}}{R_1 + R_{2//L}}$$

$$= V_{IN} \left( \frac{\frac{R_L R_2}{R_L + R_2}}{R_1 + \frac{R_L R_2}{R_L + R_2}} \right)$$

$$= V_{IN} \frac{R_L R_2}{R_1 R_2 + R_L R_1 + R_L R_2}$$

$$= V_{IN} \frac{R_2}{R_1 + R_2} \frac{R_L}{R_{1//2} + R_L}$$

$$= V_{UNLOADED} \frac{R_L}{R_{1//2} + R_L}$$

(1.7)

where  $R_{2//L}$  is the equivalent resistance of  $R_2$  and  $R_L$  in parallel,  $R_{1//2}$  is the equivalent resistance of  $R_1$  and  $R_2$  in parallel, and  $V_{UNLOADED}$  is the output voltage of the unloaded voltage divider. From the last expression it is clear that the loaded voltage is always less that the loaded voltage. The smaller the load the larger the difference between loaded and unloaded, while large load resisters do not affect the output significantly.

So, if you want to ensure that you do not affect the output of a device, you would like to have the input of your device to look like a large resistor and the output look (in this case  $R_{P:1,2}$ ) look like a small resistance. Next week we'll show that this is a general conclusion and more formally define these concepts.

## Design Exercises

Design Exercise 1-1: Use only 1 k $\Omega$  resistors to create a network with an equivalent resistance of 667 $\Omega$ . What is the minimum number of required resistors?

*Design Exercise 1-2:* Use network analysis and Ohm's Law to derive a formula for  $V_{OUT}$  for an unloaded voltage divider.

Design Exercise 1-3: Assuming that  $R_1$ ,  $R_2$  and  $R_L$  are 1 k $\Omega$  resistors and  $V_{IN}$  is 10V, compute  $V_{OUT}$  for both a loaded voltage divider and an unloaded voltage divider. How much does the output voltage change when it is loaded?

Chapter 1: DC circuit basics

# Lab 1: Voltage, Current, Resistance and Power

Your notebooks must be complete, understandable, and address all activities, design exercises, observations, and questions noted in the laboratory's procedures. Remember to use your notebook as a laboratory journal and record your data, design calculations, notes and scratch work. *Make sure to write a conclusion for each exercise and each week*.

- 1. Measure the resistances of a few resistors with an ohmmeter and see how well they match their specified values. Are they within specifications, based on their tolerance bands?

- 2. Construct the resistor network you designed in exercise 1-1. Check to see that the total resistance agrees with your calculation. Put 10V into your device and use an ammeter to see if is draws the expected current. How much power is being consumed, and how would one measure it?

- 3. Make a voltage divider from 1 -100 k $\Omega$  resistors and apply input voltages in the range of 2 V 15 V. Measure the output voltages and the current of this device. Be sure to sketch your experimental setup in your lab notebook! Plot your measurements with the voltage on the vertical axis and the current on the horizontal axis. The *equivalent* or *input resistance* of your voltage divider is the slope of the curve. Relate this to the resistors you used to construct the voltage divider.

- 4. Make your voltage divider from Exercise 1-3. Measure the output voltage and output current for a variety of load resistances. Note how the output voltage changes and compare your results to your calculations. Do the results make sense?

- 5. Learn to boot your oscilloscope and perform some basic tests. Feel free to consult the scope's manual to help you with the details as needed.

- a. Select default configuration.

- b. Connect a 10X probe to channel 1, connect the ground to the scopes test ground, and connect the probe tip to the calibration test point on the front of the scope. You should see a square wave appear with a 1 kHz frequency and 5V amplitude. Verify the operation with a 1X probe setting as well.

- c. Adjust the trim screw on the probe until the edges of the square wave are true (instead of rolling over or overshooting).

- d. Test the probe's calibration (i.e. do you get 1 kHz and a 5 V amplitude?).

- e. Zoom in and out on the signal and play with some of the measurements available to you on the scope, (including the FFT feature).

Chapter 1: DC circuit basics

# Chapter 2: Kirchhoff's Laws and Thévenin's Theorem

In this course we will be using a variety of mathematical and conceptual models to describe the electrical components and circuits that we will encounter. Ohm's Law was the first such model. In this chapter we will consolidate some of the concepts from last week into a generic model of a linear device known as a **Thévenin equivalent device** (input impedance, output impedance, and internal voltage).

The Thévenin equivalents will also be generalized and used to describe properties of signals. A **signal** will be described not only by its **voltage** but also by the **output impedance** of the device that produced or transported it. The concept of the **impedance of a signal** will be used extensively through this course as we discover various methods to transform the properties of a signal.

This week we will also examine network analysis in a complete framework known as Kirchhoff's Laws. These rules will allow us to analyze the properties of any combination of resistors and power supplies.

#### I. Kirchhoff's Laws

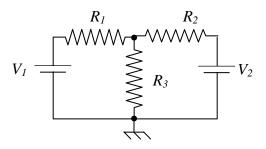

If you connect lots of power supplies and resistors together in a complicated network, then currents will flow through all the various elements so as to insure that charge is conserved, energy is conserved, and Ohm's Law is satisfied for each resistor. Simultaneously satisfying all these conditions will give you exactly one solution. The method for writing down equations to represent these conservation laws is called Kirchhoff's Laws. To explore these laws, we will consider the sample circuit shown in figure 2.1 on the right.

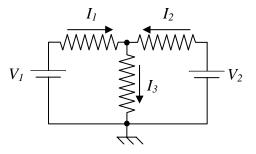

**Kirchhoff's Point Law** says that all of the current that flows into a junction must come out of the junction. This means that charge is conserved – none falls out of the circuit or pools in any location. This concept is illustrated for a junction in the example circuit (see figure 2.2). In this case, we have

$$I_1 + I_2 - I_3 = 0. (2.1)$$

**Figure 2.1**: A circuit with two power supplies and three resistors.

**Figure 2.2**: A choice of current directions for the sample circuit.

Note the sign conventions. We say that a current is positive if we define it to flow into the junction and negative if we define it to flow out the junction.

#### Kirchhoff's Loop Law

**Kirchhoff's Loop Law** says that if you sum the voltage drops around any closed loop in a circuit the total must be zero. Since the voltage drops represent the energy per unit charge, this means that all the energy which comes out of the circuit (in heating resistors, for example) must come from some power sources (such as power supplies). This is just conservation of energy.

$R_1$   $R_2$  $V_1$   $V_2$   $R_3$   $V_2$

The sign conventions are that the voltage increases across a power supply and decreases across a resistor in the direction of current

**Figure 2.3**: A choice of three Kirchhoff loops.

flow. The direction of current flow should be the same as the one defined for the Point Law. In our example circuit there are three loops that could be considered, as shown in figure 2.3, above. From these three loops, we obtain the three following relationships:

$$0 = V_1 - I_1 R_1 + I_2 R_2 - V_2$$

$$0 = V_1 - I_1 R_1 - I_3 R_3$$

$$0 = V_2 - I_2 R_2 - I_3 R_3$$

(2.2)

Any two of these relationships (since all three are not independent) and the point relationship can be used to solve for the current in each resistor and hence the power in each resistor.

It can be a real nightmare to solve more complicated networks and we will develop models and methods to avoid solving complicated networks wherever we can. We will usually do this by making one part of a circuit relatively independent of another part. Our most common use of Kirchhoff's Laws will usually be to say that V=IR and apply the simple relationships for resistors connected in series or parallel. In the next section we will begin to explore how this is possible.

## **II.** Thévenin Equivalents

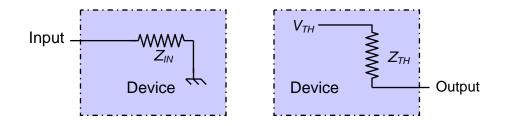

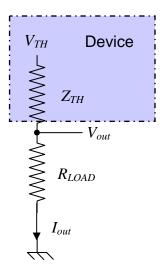

The Thévenin equivalents are models to describe the input and output properties of a device. We will assume the input of a device looks like a resistor with the other end connected to ground. We will assume that an output looks like an ideal voltage source followed by a resistor. Both of these are shown in figure 2.4, below. Note that for this week's discussion the term resistance and impedance are treated as synonymous.

One can determine the input impedance  $(Z_{IN})$  by simply applying a voltage to the input, measuring the current flowing into the device, and applying Ohm's Law.

Chapter 2: Kirchhoff's Laws and Thévenin's Theorem

**Figure 2.4**: (left) The Thévenin equivalent circuit for an input device, and (right) the Thévenin equivalent circuit for a voltage source.

Given any electrical device with two output terminals (we will assume one is called ground) there are a number of you might do to try to determine its properties:

- 1. Measure the voltage across the terminals.

- 2. Attach a resistor across the terminals and then measure the voltage.

- 3. Change the resistor and measure the voltage again, repeat.

Clearly, these are all variations on one simple measurement. What is the minimum number of measurements you must do to characterize this black box completely? Thévenin's answer is just two!

## Thévenin's Theorem

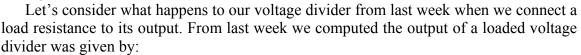

Any linear (i.e. Ohmic) system with two terminals can be completely characterized as an ideal voltage source ( $V_{TH}$  or Thévenin voltage) in series with one resistor ( $Z_{TH}$  or Thévenin resistance, and also called internal resistance sometimes). No matter what resistance ( $R_{LOAD}$ ) you connect across the two terminals, it just forms a voltage divider, as shown in fiure 2.5 on the right, and so the voltage across that load resistor is given by:

$$V_{LOAD} = V_{TH} \left( \frac{R_{LOAD}}{Z_{TH} + R_{LOAD}} \right).$$

(2.3)

A special case is when there isn't any load applied (i.e. option 1 above, where  $R_{LOAD} = \infty$ ) then the output is simply  $V_{TH}$ . From the results of these two measurements we can solve for  $R_{TH}$ .

#### Voltage Divider as a Thévenin Device

**Figure 2.5**: A voltage source connected to a load, can be treated as voltage divider

Chapter 2: Kirchhoff's Laws and Thévenin's Theorem

$$V_{LOAD} = V_{IN} \frac{R_2}{R_1 + R_2} \frac{R_{LOAD}}{R_{1//2} + R_{LOAD}}.$$

(2.4)

If we equate factors from in this relationship with the ones in the previous section, we can see that for a loaded voltage divider produces Thévenin equivalents of

$$V_{TH} = V_{IN} \frac{R_2}{R_1 + R_2}$$

and  $Z_{TH} = R_{1//2} = \frac{R_1 R_2}{R_1 + R_2}$ . (2.5, 2.6)

The relationship for  $V_{TH}$  makes sense. It is simply the unloaded output voltage as describe in the previous section. The output impedance is simply the parallel equivalent of the two resistors on the voltage divider.

#### Designing a Stiff Voltage Divider

A *stiff* output implies that the output voltage stays relatively close to its Thévenin, or unloaded, voltage when a load is implied. A rule of thumb for designing a stiff voltage source is that the output should not deviate by more than about 10% when loaded. From the relationships in the previous section, we can see that this implies that the load resistance must be more than a factor of 10 larger than the output impedance (in the voltage divider case  $R_{TH} = R_{1//2}$ ). We can think of this at a *Rule of 10*.We will usually design it so that  $R_I$  itself is smaller than the expected load by a factor of 10.

#### Generalization and Application of the Rule of 10 and Notable Exceptions

Since we are going to design and construct some very complicated circuits this year, we need to be able to focus on parts of circuits, which we will call *sub-circuits*. For example, we will often build amplifiers in three stages. The basic idea is to always insure that the downstream elements do not load the upstream elements. (1) The first stage will be a "buffer" amplifier that takes a signal and amplifies the current but not the voltage. This will allow us to connect it to the next part of the amplifier without changing (*i.e.* loading) the characteristics of whatever generated the signal. The second stage will be a voltage amplifier that amplifies a signal's voltage to whatever level we need. The final stage will be another buffer amplifier that again amplifies the current so that we will not load our voltage amplifier when we use its output.

This gains us two major advantages: We will never have a large number of interdependent simultaneous equations to solve, and our circuits will work under a wide range of differing operational conditions.

Here is the general procedure:

- Any sub-circuit can be modeled, using Thévenin's Theorem, as an ideal voltage source  $(V_{TH})$  in series with a resistance  $(R_{TH})$ .

- When we connect this to the next sub-circuit we can represent that by a load resistance  $(R_{LOAD})$  thus making a voltage divider.

- We can keep our equations simple, so that we need not employ the full Kirchhoff's Laws formalism, simply by following a "factor of 10" rule.

In summary, anything we design to produce a reliable voltage should have  $R_{TH}$  smaller  $R_{LOAD}$  by least a factor of 10. That is, we do not want the voltage to change significantly when the sub-circuit is connected to subsequent parts of the circuit.

#### **Constant Voltage Sources**

The most common sub-circuit we will use will supply a voltage to a later part of a circuit. It may be a power supply to power all the other sub-circuits, or it may be a biasing network to keep a transistor in its normal operating region. For these type sub-circuits, we want  $V_{OUT}$  to be relatively independent of  $R_L$ , so this means  $R_{LOAD} > 10R_{TH}$ .

#### **Constant Current Sources**

We will later see that transistors are current amplifiers. This means that we will often want to drive an amplifier with a current source. A current source can also be modeled as ideal voltage source in series with an  $R_{TH}$ . Again, the complete circuit will look like an ideal voltage source driving a voltage divider, but we want the current through  $R_L$  to be relatively independent of  $R_L$ . This means we want the same current as when we remove  $R_L$  and just connect (or "short") the two leads together. By applying the same logic above this implies that we want  $R_{LOAD} < 10R_{TH}$  for a stiff *current source*.

#### Impedance Matching

There are two cases when we require  $R_{LOAD} = R_{TH}$ , which we will call "impedance matching". If you want the most efficient transfer of power to your load, then you must choose  $R_{LOAD} = R_{TH}$ . By the most efficient transfer, we mean that

$$I^{2}R_{L} = \left(\frac{V_{\rm IN}}{R_{\rm L} + R_{\rm Th}}\right)^{2}R_{L}$$

(2.7)

will have its largest value when  $R_{LOAD} = R_{TH}$ . Of course this will severely load the source, dropping the output voltage by exactly a factor of two. This may, however, be fine in simple circuits – like lighting a light-bulb or driving an audio speaker.

The second case is when you have very fast signals traveling along transmission cables such as the BNC cables that we often use to connect laboratory equipment. Then, we will want to prevent reflections at our connections, since these could give rise to phony signals. Then we will want to choose  $R_{LOAD} = R_{TH}$ , even though it will decrease the amplitude of the signal. We often accomplish this matching by attaching a 50 $\Omega$  *terminator* to the end of our BNC cable to ensue that the impedance is matched.

# **Design Exercises**

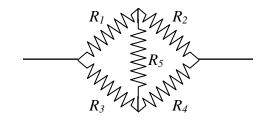

*Design Exercise 2-1:* Use Kirchhoff's laws to determine the resistance of the Wheatstone bridge depicted in the circuit in figure 2.6 on the right.

Figure 2.6: A Wheatstone bridge circuit.

Design Exercise 2-2: Find a relationship between  $V_{out}$ ,  $I_{out}$ , and  $Z_{TH}$  that does not depend on  $R_{LOAD}$  in the Thévenin equivalent circuit of figure 2.7 on the right.

*Design Exercise 2-3:* How would you measure the Thévenin resistance and voltage of a power supply?

*Design Exercise 2-4:* Prove that the power transfer from a power supply with Thévenin resistance,  $R_{Th}$ , to a load resistor,  $R_{Load}$ , is maximum when  $R_{Th}=R_{Load}$ .

**Figure 2.7**: A voltage source with load resistor.

# Lab 2: Kirchhoff, Thévenin, and Impedance Matching

1. Construct a Wheatstone bridge from 5 resistors in the 1–10 k $\Omega$  range. Measure its resistance at a few voltages (i.e. measure current and voltage). What is its resistance? Does it agree with your calculation from design exercise 2-1?

2. Construct a voltage divider similar to the one you made last week for lab exercises 1-3 and 1-4. Set  $V_{in}$  to 10 V and measure  $V_{TH}$  and  $Z_{TH}$  seen by a load resistor – you will not be able to measure  $Z_{TH}$  directly, so you will have to come up with a method for doing so (hint: the result of design exercise 2-2 can be usefully adapted to make a measurement). Do the measured  $V_{TH}$  and  $Z_{TH}$  agree with what you expect from your calculations?

3. Use your voltage divider setup from part 2. Determine experimentally the load resistance which results in the maximum output power out of the voltage divider.

4. Set the breadboard power supply to 3 V and measure  $V_{TH}$  and  $Z_{TH}$  of the breadboard power supply for this setting. Before doing your measurements, you should list the potential difficulties of such an experiment. You should also consult with the instructors before attempting it -- please do not let I<sub>out</sub> exceed 1.5 A. Comment on the engineering of the power supply.

Chapter 2: Kirchhoff's Laws and Thévenin's Theorem

# Chapter 3: Capacitors, Inductors, and Complex Impedance

In this chapter we introduce the concept of complex resistance, or impedance, by studying two reactive circuit elements, the capacitor and the inductor. We will study capacitors and inductors using differential equations and Fourier analysis and from these derive their impedance. Capacitors and inductors are used primarily in circuits involving time-dependent voltages and currents, such as AC circuits.

## I. AC Voltages and circuits

Most electronic circuits involve time-dependent voltages and currents. An important class of time-dependent signal is the sinusoidal voltage (or current), also known as an AC signal (Alternating Current). Kirchhoff's laws and Ohm's law still apply (they always apply), but one must be careful to differentiate between time-averaged and instantaneous quantities.

An AC voltage (or signal) is of the form:

$$V(t) = V_p \cos(\omega t) \tag{3.1}$$

where  $\omega$  is the angular frequency,  $V_p$  is the amplitude of the waveform or the *peak* voltage and t is the time. The angular frequency is related to the frequency (f) by  $\omega = 2\pi f$  and the period (T) is related to the frequency by T=1/f. Other useful voltages are also commonly defined. They include the *peak-to-peak voltage*  $(V_{pp})$  which is twice the amplitude and the *RMS voltage*  $(V_{RMS})$  which is  $V_{RMS} = V_p / \sqrt{2}$ . Average power in a resistive AC device is computed using RMS quantities:

$$P = I_{RMS} V_{RMS} = I_p V_p / 2. \tag{3.2}$$

This is important enough that voltmeters and ammeters in AC mode actually return the RMS values for current and voltage.

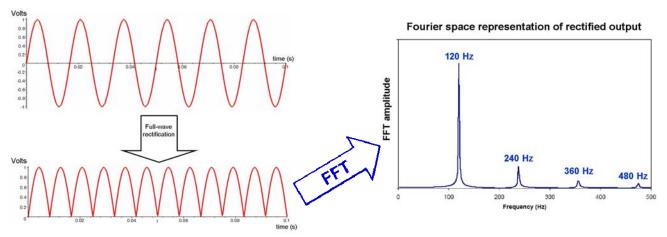

While most real world signals are not sinusoidal, AC signals are still used extensively to characterize circuits through the technique of Fourier analysis.

#### Fourier Analysis

One convenient way to characterize the rate of change of a function is to write the true function as a linear combination of a set of functions that have particularly easy characteristics to deal with analytically. In this case we can consider the trigonometric functions. It turns out that we can write any function as an integral of the form

$$V(t) = \int \widetilde{V} \cos(\omega t + \phi) d\omega$$

(3.3)

where  $\widetilde{V}$  and  $\phi$  are functions of the frequency  $\omega$ . This process is called *Fourier analysis*, and it means that any function can be written as an integral of simple sinusoidal

functions. In the case of a periodic waveform this integral becomes a sum over all the harmonics of the period (i.e. all the integer multiplicative frequencies of the period).

$$V(t) = \sum_{n} A_{n} \cos(n\omega t + \varphi_{n})$$

(3.4)

An implication of this mathematical fact is that if we can figure out what happens when we put pure sinusoidal voltages into a linear circuit, then we will know everything about its operation even for arbitrary input voltages.

#### **Complex Notation**

In complex notation we replace our sinusoidal functions by exponentials to make the calculus and bookkeeping easier still. Then we can include both phase and magnitude information. We'll define

$$e^{i\varphi} \equiv \cos\varphi + i\sin\varphi, \qquad (3.5)$$

where  $i^2 \equiv -1$ .

The general procedure for using this notation is:

- 1. Change your problem into complex algebra (i.e. replace  $\cos \omega t$  with  $e^{i\omega t}$ )

- 2. Solve the problem.

- 3. Take the real part of the solution as your answer at the end.

## **II.** Capacitors

One of the most basic rules of electronics is that circuits must be complete for currents to flow. This week, we will introduce an exception to that rule.

The capacitor is actually a small break in a circuit. Try measuring the resistance of a capacitor, you will find that it is an open circuit. However, at the inside ends of the capacitor's lead, it has little plates that act as charge reservoirs where it can store charge. For short times, you do not notice that the break is there. Negative charge initially flows in to one side and out from out the other side just as if the two leads were connected. For fast signals, the capacitor "looks" like a short-circuit. But after a while the capacitor's reservoirs fill, the current stops, and we notice that there really is a break in the circuit.

For slow signals, a capacitor "looks" like an open circuit. What is fast, and what is slow? It depends on the capacitor and the rest of the circuit. This week, you will learn how to determine fast and slow for yourselves.

Capacitors serve three major roles in electrical circuits (although all three are just variations of one basic idea):

- Charge integrators;

- High or low frequency filters;

- DC isolators.

In order to perform these functions analytically, we will need to introduce a number of new concepts and some significant mathematical formalism. In this process we will also develop a number of new concepts in analyzing electronic circuits.

#### Capacitance

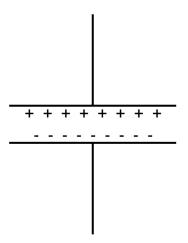

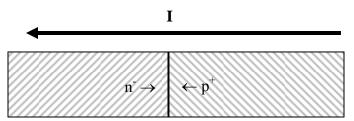

A capacitor is a device for storing charge and electrical energy. It consists of two parallel conducting plates and some non-conducting material between the plates, as shown in figure 3.1 on the right. When voltage is applied positive charge collects on one plate and negative charge collects on the other plane. Since they are attracted to each other this is a stable state until the voltage is changed again.

A capacitor's charge capacity or *capacitance* (*C*) is defined as:

$$Q = CV \tag{3.6}$$

which relates the charge stored in the capacitor (Q) to the voltage across its leads (V). Capacitance is measured in Farads (F). A Farad is a very large unit and most applications use  $\mu$ F, nF, or pF sized devices. Many electronics components have small parasitic capacitances due to their leads and design.

**Figure 3.1**: A capacitor consist of two parallel plates which store equal and opposite amounts of charge

The capacitor also stores energy in the electric field generated by the charges on its two plates. The potential energy stored in a capacitor, with voltage V on it, is

$$E = \frac{1}{2}CV^2 \tag{3.7}$$

We usually speak in terms of current when we analyze a circuit. By noting that the current is the rate of change of charge, we can rewrite the definition of capacitance in terms of the current as:

$$V = \frac{1}{C}Q = \frac{1}{C}\int Idt$$

(3.8)

or

$$I = C\frac{dV}{dt} = C\dot{V}$$

(3.9)

This shows that we can integrate a function I(t) just by monitoring the voltage as the current charges up a capacitor, or we can differentiate a function V(t) by putting it across a capacitor, and monitoring the current flow when the voltage changes.

## A Simple RC Circuit

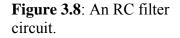

We will start by looking in detail at the simplest capacitive circuit, which is shown in figure 3.2 on the right. An RC circuit is made by simply putting a resistor and a capacitor together as a voltage divider. We will put the resistor in first, so we can connect the capacitor to ground.

By applying Kirchhoff's Laws to this circuit, we can see that:

- 1. The same current flows through both the resistor and the capacitor, and

- 2. The sum of the voltage drops across the two elements equal the input voltage.

**Figure 3.2**: A simple RC circuit which integrates current.

This can be put into a formula in the following equation:

$$V_{IN} = IR + \frac{1}{C} \int Idt \,. \tag{3.10}$$

which can also be written as

$$\frac{V_{IN}}{R} = I + \frac{1}{RC} \int I dt \,. \tag{3.11}$$

We can also put this into the form of a differential equation in the following way:

$$\frac{dV_{IN}}{dt} = R\frac{dI}{dt} + \frac{I}{C}$$

(3.12a)

or

$$C\dot{V}_{IN} = R\dot{CI} + I. \tag{3.12b}$$

These equations show that times are measured in units of *RC*, and that what you see depends on how quickly things change during one *RC* time interval.

If the current changes quickly, then most of the voltage will show up across the resistor, while the voltage across the capacitor slowly charges up as it integrates the current. If the voltage changes slowly, then most of the voltage shows up across the capacitor as it charges. Since this usually requires a small current, the voltage across the resistor stays small.

But, what happens at intermediate times? To determine this quantitatively we will have to develop some more sophisticated mathematical techniques.

#### Solutions to RC Circuit

Rather than produce the general solution, we will concentrate on two special cases that are particularly useful. The first will be for a constant voltage and the second will be a sinusoidal input.

Chapter 3: Capacitors, Inductors, and Complex Impedance

To study a constant supply voltage on an RC circuit, we set the left side of equation 3.12 equal to a constant voltage. Then we have a simple homogeneous differential equation with the simple solution for the current of a decaying exponential,

$$I = I_0 e^{-t/(RC)}, (3.13)$$

which will account for any initial conditions. After a time of a few RC time periods, this solution will have decayed away to the supply voltage.

And now let us consider the other solution. In the prior section, we argued that if we can understand the RC circuit's behavior for sinusoidal input we can deal with any arbitrary input. Therefore, this is the important one.

Let's look at our simple *RC* circuit and suppose that we apply (or drive) a simple sine wave into the input:

$$V_{IN} = V_0 \cos(\omega t). \tag{3.14}$$

In complex notation, this means that we will set the drive voltage to

$$V_{IN} = V_0 \exp(i\omega t), \tag{3.15}$$

and we just have to remember to take the Real part at the end of our calculation.

If we put this drive voltage into the differential equation (equation 3.12), then it becomes a relatively simple inhomogeneous differential equation:

$$C\frac{dV_{IN}}{dt} = CV_0 i\omega \exp(i\omega t) = RC\frac{dI}{dt} + I.$$

(3.16)

This is relatively simple because it shows up so often in physics that you might as well memorize the solution or at least the way to get the solution. Note that mathematically it looks just like a driven harmonic oscillator.

We can obtain the solution by using the standard recipe for first order linear differential equations. We start by rewriting equation as

$$\frac{dI}{dt} + \frac{1}{RC}I = \frac{i\omega V_0}{R}\exp(i\omega t), \qquad (3.17)$$

which we then multiply by  $\exp(t/RC)$  to obtain

$$\exp(t/RC)\frac{dI}{dt} + \frac{\exp(t/RC)}{RC}I = \frac{i\omega V_0}{R}\exp[(i\omega + \frac{1}{RC})t].$$

(3.18)

The left hand-side of this equality can be rewritten under the form of a total derivative (multiplication rule) so that we now have

$$\frac{d}{dt}\left[I(t)\exp(\frac{t}{RC})\right] = \frac{i\omega V_0}{R}\exp[(i\omega + \frac{1}{RC})t].$$

(3.19)

This equation is easily integrable and can be rewritten as

$$I(t)\exp(\frac{t}{RC}) = \frac{i\omega V_0}{R} \int \exp[(i\omega + \frac{1}{RC})t]dt .$$

(3.20)

Chapter 3: Capacitors, Inductors, and Complex Impedance

The integral is straightforward and yields the following expression:

$$I(t) = \frac{i\omega V_0}{R} \frac{1}{\frac{1}{R_C} + i\omega} \exp(i\omega t) + Cst \cdot \exp(-\frac{t}{RC})$$

(3.21)

The first term represent the "steady state" oscillatory behavior of the driven circuit, while the second term describes the transient behavior of the current after switching on the driving voltage. Since we are only interested in the long-term behavior of the circuit, we neglect the second term and concentrate on the first. After a little bit of algebra, we can rewrite the steady-state current as

$$I(t) = \frac{i\omega V_0}{R} \frac{1}{V_{RC} + i\omega} \exp(i\omega t) = \frac{\omega V_0 C}{\sqrt{1 + (\omega RC)^2}} \frac{\omega RC + i}{\sqrt{1 + (\omega RC)^2}} \exp(i\omega t)$$

(3.22)

The second fraction can be interpreted as a phase term with  $\tan \phi = \frac{1}{\omega RC}$ , so that the expression for the current becomes

$$I(t) = I_0 \exp(i\omega t + \phi)$$

(3.23)

with

$$I_{0} = \frac{\omega V_{0}C}{\sqrt{1 + (\omega RC)^{2}}} = \frac{V_{0}}{R} \cos(\phi)$$

(3.24)

The real solution of this simple RC circuit can be obtained by taking the real part of equation 23, and is left as an exercise to the reader.

The solution of the simple RC circuit appears to be rather complicated and involved, however it simplifies considerably when we plug equation 23 back in to the original integral equation from Kirchhoff's loop law (equation 10). After integrating the exponential and a little bit of algebra, we obtain

$$V_{in}(t;\omega) = I(t)R + I(t)\frac{1}{i\omega C}$$

(3.25)

This remarkably simple expression looks a lot like the standard Kirchhoff's loop law for resistors, except that the capacitor term behaves with a frequency dependent "imaginary" resistance.

#### RC Impedance

We will obtain the same solution as the one we obtained for the original voltage divider, as long as we assign an imaginary, frequency dependent, resistance to the capacitor. The "imaginary" part just means that it will produce a  $\pi/2$  phase shift between the voltage and the current for a sinusoidal input. We will call this impedance

$$Z_C = \frac{1}{i\omega C}.$$

(3.26)

Now, the solution for an *RC* divider becomes somewhat simplified. We can compute the total current flowing through the circuit as

$$I = \frac{V_{in}}{Z_{tot}} = \frac{V_{in}}{R + Z_C} = \frac{V_0 e^{i\omega t}}{R + 1/(i\omega C)} = \frac{i\omega C V_0 e^{i\omega t}}{1 + i\omega R C} = \frac{V_0}{R} \frac{i\omega R C_0 e^{i\omega t}}{(1 + i\omega R C)} = \frac{V_0}{R} \cos(\phi) e^{i(\omega t + \phi)}$$

(3.27)

The voltage across an element is just this current times the element's impedance. For the voltage drop across the resistor it is largely the same as before:

$$V_R = IR = V_0 \cos(\phi) e^{i(\omega t + \phi)}.$$

(3.28)

For the capacitor, we get the following voltage drop:

$$V_{C} = IZ_{C} = I \frac{1}{i\omega C} = \frac{V_{0} \cos(\phi)e^{i(\omega t + \phi)}}{i\omega RC} = -iV_{0} \sin(\phi)e^{i(\omega t + \phi)}$$

$$= V_{0} \frac{\cos(\phi)}{\omega RC} e^{i(\omega t + \phi - \pi/2)} = V_{0} \sin(\phi)e^{i(\omega t + \phi - \pi/2)}$$

(3.29)

If everything is correctly calculated then the sum of the voltage drops across the two elements should be equal to the input voltage. Let's try it:

$$V_{R} + V_{C} = V_{0} (\cos(\phi) - i\sin(\phi)) e^{i(\omega t + \phi)} = V_{0} e^{-i\phi} e^{i(\omega t + \phi)} = V_{0} e^{i\omega t}$$

(3.30)

Remember, you get the actual waveforms by taking the real parts of these complex solutions. Therefore

$$V_R = V_0 \cos\phi \cos(\omega t + \phi) \text{ and}$$

(3.31)

$$V_C = V_0 \sin\phi \cos(\omega t + \phi - \pi/2) = -V_0 \sin\phi \sin(\omega t + \phi)$$

(3.32)

This looks complicated, but the limits of high frequency and low frequency are easy to remember. At high frequencies ( $\phi \rightarrow 0$ ), the capacitor is like a short, and all the voltage shows up across the resistor. At low frequencies ( $\phi \rightarrow \pi/2$ ), the capacitor is like an open circuit, and all the voltage shows up across the capacitor.

If you consider the leading terms for the elements with the small voltages, you find that

$$V_{C} = V_{0} \frac{(1 - i\omega RC)}{1 + (\omega RC)^{2}} \rightarrow -\frac{i}{\omega} \left(\frac{V_{0}}{RC}\right) \text{ as } \omega \rightarrow \infty$$

$$V_{R} = V_{0} \frac{\omega RC(i + \omega RC)}{1 + (\omega RC)^{2}} \rightarrow i\omega (RCV_{0}) \text{ as } \omega \rightarrow 0$$

(3.33)

Thus, at high frequency, the voltage across the capacitor is the integral of the input voltage, while at low frequency the voltage across the resistor is the derivative of the input voltage.

This says that as long as all the important frequencies are high, the capacitor will integrate the input voltage. If all the important frequencies are small, the resistor will differentiate the voltage. If there are intermediate frequencies, or a mixture of some high

and some low frequencies, the result will not be so simple but it can be determined from the voltage divider algebra using complex notation.

We finish by noting that the voltage on the capacitor is always  $-\pi/2$  out of phase with the voltage on the resistor.

## **III. Inductors**

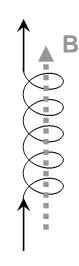

An inductors is a coil of wire, or solenoid, which can be used to store energy in the magnetic field that it generates (see figure 3.3 on the right). It is mathematically similar to a capacitor, but has exactly the opposite behavior: it behaves as a short circuit for low frequencies and as an open circuit for high frequencies (i.e. it passes low frequency signals and blocks high frequency signals).

The energy stored in the field of an inductor with inductance L is given by the following formula:

$$E = \frac{1}{2}LI^2$$

(3.34)

The SI unit of inductance is the Henry (H). Commercially available inductors have inductances that range from nH to mH. Small millimeter-size and centimeter size solenoids typically have inductances in the range of  $\mu$ H, while magnetic field coils can have a inductances in the mH range, and can sometimes have inductances of up to several H. Most electronics components have small parasitic inductances due to their leads and design (for example, wire-wound power resistors).

In an electric circuit, a voltage, or electromotive potential, is generated across the terminals of the inductor when the current changes due to Faraday's law. The voltage drop is given by the following simple expression:

$$V = L \frac{dI}{dt}$$

(3.35)

From this equation, we see that the inductor operates exactly opposite to a capacitor: an inductor differentiates the current and integrates the voltage.

## The LR circuit

We can analyze the LR circuit in much the same way that we derived the operation of the RC circuit. We start by applying Kirchhoff's loop law to the LR circuit in figure 3.4 below, and we find that

**Figure 3.3**: An inductor consists of a coiled wire, also called a solenoid. The dashed arrow "B", represent the magnetic field generated by the current in the inductor.

Chapter 3: Capacitors, Inductors, and Complex Impedance

$$V_{IN} = IR + L\frac{dI}{dt}.$$

(3.36)

If we apply a constant voltage the solution can be calculated using the techniques developed for the RC circuit and we calculate that

$$I(t) = I_0 \left( 1 - \exp(-\frac{R}{L}t) \right).$$

(3.37)

The circuit approaches the steady state current  $I_0 = V_{IN}/R$  with a time constant of L/R.

**Figure 3.4**: A simple LR circuit.

#### LR impedance

Instead of solving the differential equation for the LR circuit with a sinusoidal applied input voltage such as that given by equations 14 and 15, as we did with the RC circuit, we will just assume that the current has the form

$$I(t) = I_0 \exp(i\omega t + \phi) \tag{3.38}$$

We plug this ansatz solution back into the differential equation of equation 31 and find that

$$V_{N} = I(t)R + i\omega LI , \qquad (3.39)$$

from which we deduce that the inductor behaves as a resistor with frequency dependent "imaginary" resistance. The impedance of an inductor is therefore

$$Z_L = i\omega L \tag{3.40}$$

Just as with the RC circuit, we can apply Ohm's law to the circuit to calculate the total current. Since R and L are in series, we obtain

$$I(t) = \frac{V_{in}}{Z_{total}} = \frac{V_0 e^{i\omega t}}{R + Z_L} = \frac{V_0 e^{i\omega t}}{R + i\omega L} = \frac{V_0}{R} \frac{1 - i\omega \frac{L}{R}}{1 + \left(\omega \frac{L}{R}\right)^2} e^{i\omega t} = \frac{V_0}{R} \cos(\phi) e^{i(\omega t - \phi)}$$

(3.41)

where the phase is given by  $\tan(\phi) = \omega \frac{L}{R}$ . We calculate the voltage drop across the resistor using the expression for the current and find that

$$V_R = I(t)R = V_0 \cos(\phi)e^{i(\omega t - \phi)}$$

(3.42)

The voltage drop across the inductor is calculated the same way, and we find

$$V_{L} = i\omega LI(t) = i\omega L \frac{V_{0}}{R} \cos(\phi) e^{i(\omega t - \phi)} = iV_{0} \sin(\phi) e^{i(\omega t - \phi)} = V_{0} \cos(\phi) e^{i(\omega t - \phi + \pi/2)}$$

(3.43)

If everything is correctly calculated then the sum of the voltage drops across the two elements should be equal to the input voltage. Let's try it:

$$V_{R} + V_{L} = V_{0} (\cos(\phi) + i\sin(\phi)) e^{i(\omega - \phi)} = V_{0} e^{i\phi} e^{i(\omega - \phi)} = V_{0} e^{i\omega t}$$

(3.44)

You get the actual waveforms by taking the real parts of these complex solutions. Therefore

$$V_R = V_0 \cos\phi \cos(\omega t - \phi) \text{ and}$$

(3.45)

$$V_L = V_0 \sin\phi \cos(\omega t - \phi + \pi/2) = V_0 \sin\phi \sin(\omega t - \phi)$$

(3.46)

This looks complicated, but the limits of high frequency and low frequency are easy to remember. At high frequencies ( $\phi \rightarrow \pi/2$ ), the inductor is like an open circuit, and all the voltage shows up across the inductor. At low frequencies ( $\phi \rightarrow 0$ ), the inductor is like a short circuit or just a plain wire, and all the voltage shows up across the resistor.

It should also be pointed out that the voltage on the inductor is always  $+\pi/2$  out of phase with the voltage on the resistor.

## **IV.** Transformers

Transformers are an ingenious combination of two inductors. They are used to transfer power between two circuits by magnetic coupling. The transformer changes an input voltage, without affecting the signal shape, similar to the voltage divider of last week. However it has several important differences:

- It can increase as well as decrease a signal's amplitude (i.e. AC voltage).

- It requires a time-varying (AC) input to work.

- It is much harder to fabricate.

- It usually does not work well for very fast signals (since inductors block high frequencies).

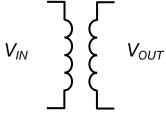

**Figure 3.5**: The schematic symbol for a transformer.

Transformers are commonly used as a major component in a DC power supplies since they can convert a 120 V AC wall voltage into a smaller voltage

that is closer to the desired DC voltage (e.g. 5 V or  $\pm 15$  V). The schematic symbol for a transformer is shown in figure 3.5, above.

Transformers are passive devices that simultaneously change the voltage and current of a circuit. They have (at least) four terminals: two inputs (called the primary) and two outputs (called the secondary). There is no real difference between the input and output for a transformer, you could simply flip it around and use the secondary as the input and the primary as the output. However, for the sake of clarity, we will always assume that you use the primary for input and the secondary for output. The coupling between the input and output is done magnetically. This allows transformers to have a number of interesting benefits including:

- There is no DC connection between input and output, so transformers are often used to isolate one circuit from another.

- Transformers only work for time varying signals, when the inductive coupling between the coils is greater than the resistive losses.

Since they have no external power the output power can not be greater than the input power

$$P = V_{\rm p}I_{\rm p} \ge V_{\rm s}I_{\rm s} \,. \tag{3.47}$$

Usually, we will assume equality but there are small resistances (and hence resistive losses) in the coils and a poorly or cheaply designed transformer many not have the input and output sufficiently strongly coupled to each other. Depending on the device and the signal the output power may well be less than the input power.

Transformers are most commonly used to change line voltage (120 V RMS at 60 Hz) into a more convenient voltage. High power transmission lines use transformers to increase the voltage and decrease the current. This reduces  $I^2R$  power losses in the transmission wires. For our circuits we will use a transformer that reduces the voltage and increases the current.

Transformers are characterized by the ratio of the number of turns on the input and output windings. The magnetic coupling in an ideal transformer will insure that the number of turns times the current flowing is the same for the input and output:

$$N_{\rm p}I_{\rm p} = N_{\rm s}I_{\rm s} \Longrightarrow \frac{I_{\rm s}}{I_{\rm p}} = \frac{N_{\rm p}}{N_{\rm s}}$$

(3.48)

Since the voltage must change in the opposite manner to keep the input and output power, the ratio of the voltages is the same as the ratio of the turns:

$$\frac{V_{\rm s}}{V_{\rm p}} = \frac{N_{\rm s}}{N_{\rm p}} \tag{3.49}$$

Transformers are usually called step-up or step-down according to whether the output voltage increases or decreases.

A transformer also transforms the impedance of a circuit, since it changes the ratio of V/I. Using our rules above, the ratio of output impedance to input impedance is the square of the ratio of turns:

$$\frac{Z_{\rm s}}{Z_{\rm p}} = \frac{V_{\rm s}}{I_{\rm s}} \frac{I_{\rm p}}{V_{\rm p}} = \left(\frac{N_{\rm s}}{N_{\rm p}}\right)^2 \tag{3.50}$$

So, if you use a transformer as a step-up transformer, it increases the voltage and the impedance at its output relative to its input. If you use a transformer as a step-down transformer, it decreases the voltage and the impedance at its output.

# **Design Exercises**

**Design Exercise 3-1:** Using Kirchhoff's laws, derive a formula for the total capacitance of two capacitors in parallel and a formula for the total capacitance of two capacitors in series.

**Design Exercise 3-2:** Using Kirchhoff's laws, derive a formula for the total inductance of two inductors in parallel and a formula for the total inductance of two inductors in series.

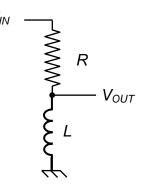

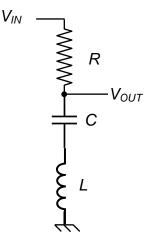

**Design Exercise 3-3:** Calculate  $V_{out}$  as a function of  $V_{in}$  in the RLC circuit of figure 3.6 on the right, using the formulas for  $Z_R$ ,  $Z_C$ , and  $Z_L$  (do not use Maple / Mathematica / MATLAB / MathCad for these calculations and show all steps).  $V_{in}$  is a perfect AC voltage signal with a frequency of  $\omega$ .

Plot the magnitude and phase of V<sub>out</sub> as a function of  $\omega$  for R = 1 k $\Omega$ , C = 1  $\mu$ F, and L = 10  $\mu$ H. What happens to the magnitude and the phase of V<sub>out</sub> at  $\omega = 1/\sqrt{LC}$ ?

(Maple / Mathematica / MATLAB / MathCad are permitted for the plots.)

**Figure 3.6**: An RLC filter circuit.

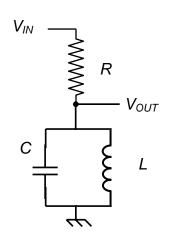

**Design Exercise 3-4:** Calculate  $V_{out}$  as a function of  $V_{in}$  in the RLC circuit depicted on the right, using the formulas for  $Z_R$ ,  $Z_C$ , and  $Z_L$  (do not use Maple / Mathematica / MATLAB / MathCad for these calculations and show all steps).  $V_{in}$  is a perfect AC voltage signal with a frequency of  $\omega$ .

Plot the magnitude and phase of V<sub>out</sub> as a function of  $\omega$  for R = 1 k $\Omega$ , C = 1  $\mu$ F, and L = 10  $\mu$ H. What happens to the magnitude and the phase of V<sub>out</sub> at  $\omega = 1/\sqrt{LC}$ ?

(Maple / Mathematica / MATLAB / MathCad are permitted for the plots.)

**Figure 3.7**: Another RLC filter circuit.

# Lab 3: AC signals, Complex Impedance, and Phase

## Section 1: Introduction to transformers

In this section, we use a transformer to change the impedance of an AC signal.

**1a.** Measure the **output impedance** of a signal generator with a 0.5V amplitude sinusoid output of 1 kHz and the input impedance of a speaker. Remember you are using AC signals. What does an AC current reading from a DVM mean in terms of the waveform? How do you measure current with an oscilloscope? Check this with the oscilloscope.

**1b.** Connect the signal generator to a speaker and measure the signal amplitude with, and without connecting to the speaker. The voltage drops so much because of the impedance mismatch. Measure the power into the speaker.

**1c.** Use a transformer to decrease the output voltage, while increasing the output current into the speaker. Measure  $V_{out}$ ,  $V_{in}$ ,  $I_{in}$ , and  $I_{out}$ . How well does the transformer transmit power? Does  $V_{out}/V_{in} = I_{in}/I_{out}$ ? Estimate the ratio of primary turns to secondary turns?

**1.d** Measure the **output impedance** of the signal generator plus transformer circuit. Does the measured value agree with what you expect theoretically?

## Section 2: The RC circuit

In this section, we take a first look at the classic RC circuit and the concept of phase.

**2a.** Get two capacitors and measure their individual capacitances. Measure the total capacitance with a capacitance meter when they are in series, and when they are in parallel. Do you get good agreement with what you expect?

**2b.** Construct the RC circuit to the right, with component ranges R=1-10 k $\Omega$  and C=0.001-0.01  $\mu$ F. Set the function generator at approximately  $\omega$ =0.1/RC with a square wave and describe what you see. Measure the time constant of the exponential and use it to determine the capacitance of C (R should be determined with a multimeter).

**2c.** (Same set-up) Set the function generator to sinusoidal output at  $\omega$ =1/RC and measure the magnitude of V<sub>in</sub> and V<sub>out</sub>. Do you get what you expect ? Measure the phase of V<sub>out</sub> with respect to V<sub>in</sub> and make a Lissajou plot of V<sub>out</sub> and V<sub>in</sub>.

Chapter 3: Capacitors, Inductors, and Complex Impedance

# **Chapter 4: Passive Analog Signal Processing**

In this chapter we introduce filters and signal transmission theory. Filters are essential components of most analog circuits and are used to remove unwanted signals (i.e. noise) from the actual signal. Transmission lines are essential for sending signals from one device to another, such as from a detector to a data acquisition module.

## I. Filters

Filters are ubiquitous in analog electronic circuitry. In fact, if you see a capacitor or an inductor in a circuit there is a good chance it is part of a filter. Filters are frequently used to clean up (i.e. remove high frequency noise) power supplies and remove spurious frequencies from a signal (frequently 60 Hz, switching power supply noise in computers, display screen noise, ground loop noise, and Radio-Frequency (RF) pick-up).

## A. RC Filters:

RC filters are by far the most common filters around. They are simple to make (i.e. just a resistor and a capacitor), reliable, and involve relatively simple design calculations.

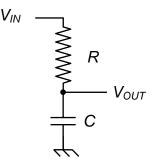

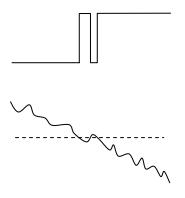

#### 1. The Low-Pass RC Filter

$V_{out} = V_C = V_0 \sin(\phi) e^{i(\omega t + \phi - \pi/2)}$

The low-pass RC filter, or integrator, is used to remove high frequencies from a signal. Applications include the removal of RF pick-up noise and reducing ripple voltages on power supplies.

A generic RC low pass filter circuit is shown in figure 4.1 on the right. We have already calculated its performance in the previous chapter using Fourier analysis and complex impedances. We recall the results (equation 28):

Where  $\sin(\phi) = 1/\sqrt{1 + (\omega RC)^2}$  and  $V_{in} = V_0 e^{i\omega t}$ . From these quantities we can compute the gain and phase performance of the filter. The gain is defined as  $Gain = |V_{out}/V_{in}|$  and the phase as  $\varphi = \phi - \pi/2$  (this is just the part after the  $\omega t$  in the exponent).

(4.1)

The RC filter is just a voltage divider with complex impedances, so we can calculate the gain easily:

Chapter 4: Passive Analog Signal Processing

$$\left|\frac{V_{out}}{V_{in}}\right| = \left|\frac{1/i\omega C}{R+1/i\omega C}\right| = \left|\frac{1}{1+i\omega RC}\right| = \frac{1}{\sqrt{1+(\omega RC)^2}} = \sin(\phi)$$

(4.2)

The phase of the output voltage with respect to the input is easily computed and is given by

$$\tan \varphi = \tan(\phi - \pi/2) = \cot(\phi) = \omega RC \tag{4.3}$$

At  $\omega = 1/RC$ , the output voltage drops to  $1/\sqrt{2}$  of the input voltage, and consequently the power transmission drops to 50% or  $-3dB^1$ . At this frequency, the voltage across the resistor and the voltage across the capacitor are equal in amplitude, but  $\pm \pi/2$  out of phase with the drive voltage. The average value of  $V^2$  across either the resistor or the capacitor is down by a factor of 2 from the drive voltage. Consequently, this frequency characterizes the *RC* circuit completely and is called the 3dB frequency. We can rewrite the gain and phase equations in terms of the 3dB frequency:

$$gain = \frac{1}{\sqrt{1 + (f / f_{3dB})^2}}$$

(4.4),  $\tan \varphi = f / f_{3dB}$ (4.5)

with  $f_{3dB} = 1/2\pi RC$ .

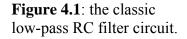

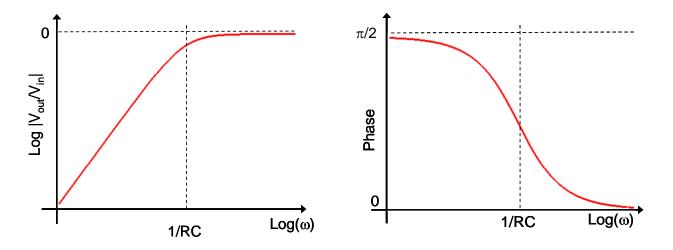

The Bode plots (log-log or semi-log plots) for the gain and phase of the low pass filter are shown in figure 4.2, below.

**Figure 4.2**: Bode plots of the relative magnitude (left) and phase (right) of the output of an RC low-pass filter.

$$dB = 20\log_{10}(V/V_0)$$

So at -3dB, the voltage (or current) has dropped to  $1/\sqrt{2}$  of its input value.

<sup>&</sup>lt;sup>1</sup> A dB or decibel is a notation for quantifying a ratio of two numbers. For power, a dB is defined as  $dB = 10log_{10}(P/P_0)$

From this definition we can see that a ratio of 0.5 is roughly -3. Hence -3db is the same as halving a signal. For voltage or current, a dB is defined as

Past the -3 dB point, the log-log "slope" for the gain is -20 dB/Decade or -6 dB/Octave. The low-pass RC filter is also called an integrator because it integrates currents with frequencies above  $f_{3dB}$ . In other words  $V_{out} = \frac{1}{C} \int I(t) dt$  (see chapter 3, equation 8) for currents with frequency components above  $f_{3dB}$ .

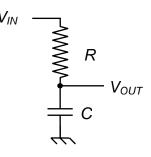

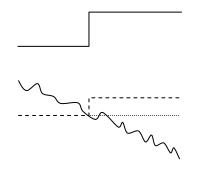

#### 2) The High-Pass RC Filter

The high-pass RC filter, or differentiator, is used to remove low frequencies from a signal. Applications include the removal of DC bias voltages and 60 Hz pick-up voltages.

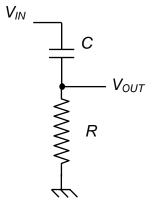

A generic RC high-pass filter circuit is shown in figure 4.3 on the right. Mathematically, high-pass filter can be treated the same way a their low pass cousins: they are almost identical except that Vout measures the voltage drop across the resistor instead of the capacitor. Qualitatively, the capacitor blocks DC and low frequency signals.

If we treat the high-pass filter as a complex impedance voltage divider, then we obtain immediately

**Figure 4.3**: the classic high-pass RC filter circuit.

$$\left|\frac{V_{out}}{V_{in}}\right| = \left|\frac{R}{R+1/i\omega C}\right| = \left|\frac{i\omega RC}{1+i\omega RC}\right| = \frac{\omega RC}{\sqrt{1+(\omega RC)^2}} = \cos(\phi)$$

(4.6)

$$\tan \varphi = 1/\omega RC$$

(4.7)

We can rewrite these using only  $f_{3dB}$  to produce more compact design equations:

$$gain = \frac{(f / f_{3dB})}{\sqrt{1 + (f / f_{3dB})^2}}$$

(4.8),  $\tan \varphi = f_{3dB} / f$ (4.9)

The Bode plots (log-log or semi-log plots) for the gain and phase of the high-pass filter are shown in figure 4.4, below.

## 3) RC Filter Design

. . .

When designing an RC filter, you need to think about two things:

- 1. Choose an appropriate  $f_{3dB}$ .

- 2. Make sure the impedance is appropriate for your desired output load.

Step 1 is straightforward and depends on the frequencies you want to pass and block.

In Step 2 you pick R so as to satisfy the impedance requirements of your signal source and your signal destination. Typically, the signals we want to pass are around  $f_{3dB}$ , so the impedance of the capacitor and the impedance of the resistor will be about the same.

**Figure 4.4**: Bode plots of the relative magnitude (left) and phase (right) of the output of an RC high-pass filter.

When filtering an input, choose the resistance to be about 10 times smaller than the input impedance of the next stage. This will prevent the next stage from loading the filter. You would also like to choose the resistance to be at least 10 times larger than the previous stage of your circuit's output impedance.

Choose the capacitor for the appropriate  $f_{3dB} = 1/(2\pi RC)$ .

- If the signal you want to pass is low frequency, choose  $f_{3dB} \approx 2 f_{Pass}$ , and hence  $C \approx 1/(4\pi R f_{Pass})$ .

- If the signal you want to pass is high frequency, choose  $f_{3dB} \approx f_{Pass}/2$ , and hence  $C \approx 1/(\pi R f_{Pass})$ .

## 3) Combination Filters

If you put several RC filters in a row you can make a more sophisticated signal filter. For example, several similar low-pass filters placed on after the other will produce a steeper fall off of the gain. One can also use a low-pass followed by a high pass to produce a bandpass filter ( $f_{3dB,lowpass} > f_{3dB,highpass}$ ).

**Design tip:** When you are designing a bandpass filter, you should make sure that the resistor in the second stage is larger than the first stage by about a factor of 10. Otherwise, the second stage will load the first stage, and shift the effective  $f_{3dB}$  frequency of the first stage.

## 4) Applications

Here are some specific applications of RC filters:

#### **Blocking Capacitor**

This is a high pass filter that is used to eliminate DC. Suppose that you want to measure small time-dependent signals that happen to "float" on a high voltage. If you use a blocking capacitor, then the high voltage DC will not get through to your detection electronics, but the signal will get through. Choose  $f_{3dB}$  low to insure that your entire signal gets through.

#### **Ripple Eliminator**

This is a low pass filter used to build power supplies. Since most of our power is 60 Hz AC, our DC power supplies will convert AC to DC, but there will always be some residual 60 Hz "ripple". A low pass filter with  $f_{3dB}$  set well below 60 Hz will work. You do not use a resistance in this case, but let the combination of the loading resistance  $R_L$  and the Thevenin resistance of the previous components serve as your R. This usually requires a large capacitor since  $R_L$  might be quite small when you use the power supply. If the capacitor is not big enough, then  $f_{3dB}$  will then shift to a higher frequency, and the 60 Hz ripple will reappear.

#### Chip Supply Clean Up

Frequently the voltage which you supply to a chip component, such as an op-amp (we will study these later in the semester), may be "clean" when it comes out of the power supply, but will pick up noise by the time it reaches the component. In this case a 10 - 100 nF capacitor placed at the supply leads of the component will remove the high frequency pick-up noise.

#### Noise Eliminator

Any signal line is susceptible to picking up high frequency transients; especially if there are motors or switching power supplies (or FM radio stations!) nearby. A noise eliminator is a low pass filter with a high value of  $f_{3dB}$ .

#### Integrator

If you build an RC filter, but set the value of  $f_{3dB}$  much higher than the highest frequency in your signal, the filter integrates your signal. From our earlier analysis, when  $f \ll f_{3dB}$ , we can see that each (low) frequency voltage component will see a  $\pi/2$  same phase shift and its amplitude will be proportional to 1/f. This is exactly the prescription for integration. So, a high pass filter sends high frequencies out on the resistor, and the integral of very low frequencies on the capacitor.

#### Differentiator

If you build an RC filter with  $f_{3dB}$  lower than the lowest frequency in your signal, the filter differentiates your signal. From our earlier analysis, when  $f >> f_{3dB}$ , each (high) frequency voltage component will see a  $\pi/2$  same phase shift and its amplitude will be proportional to f. This is exactly the prescription for differentiation. So, a low pass filter sends low frequencies out on the capacitor, and the derivative of high frequencies on the resistor.

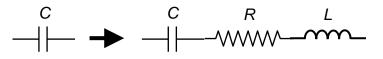

## 5. High frequency performance of capacitors

In principle, one could use an LR (inductor-resistor) circuit instead of an RC circuit to make low-pass and high-pass filters and obtain similar performance. However, in practice generally avoids inductors if possible. Inductors tend to be physically larger, more expensive, and deviate further from ideal performance than capacitors.

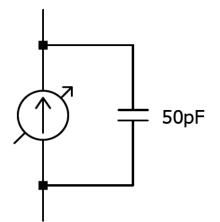

While capacitors generally offer superior performance to inductors, they also show significant deviations from the ideal  $Z = 1/i\omega C$  impedance at high frequencies. Capacitors will generally have a little bit of spurious resistance (i.e. like a resistor) and inductance (i.e. like an inductor) at high frequencies. In fact, circuit designers will often model a real capacitor with the following simple circuit, though more complex circuits are sometimes necessary:

**Figure 4.5**: A real capacitor can be modeled as an ideal capacitor in series with some small resistor and inductor.

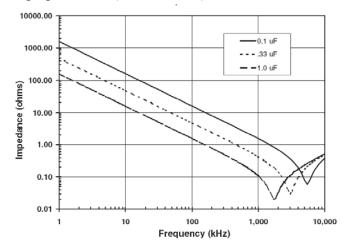

The resistance is due to the non-zero high frequency conductivity of the dielectric material separating the two conductor plates of the capacitor. The inductance is due to two effects: 1) the design of the capacitor, especially the leads, will contribute inductance., and 2) Maxwell's equations for electrodynamics require that a capacitor have an inductance at high frequencies<sup>2</sup>. Capacitor manufacturer will provide the specifications for the spurious resistance and inductance of their capacitors. The plot in figure 4.6, below, shows the frequency dependence of the impedance of a Cornell Dubilier acrylic surface mount film capacitor.

A common remedy for dealing with the inherent inductance of a capacitor at high frequencies is to place a small capacitor (10 - 100 pF) in parallel with the main capacitor in RC filter. The high frequency performance of the small capacitor will generally much better than that of the main capacitor: the small will pick-up the high frequency signal when the main, larger capacitor begins to have a significant inductance. The gain fall-off

<sup>&</sup>lt;sup>2</sup> The Feynman Lectures on Physics, Vol. 2, by R. P. Feynman, R. B. Leighton, and M. Sands, p. 23-2.

of the RC filter will no longer be -20 dB/decade, but at least a low-pass filter will not start to behave like a high-pass filter (or vice-versa)!

**Figure 4.6**: Impedance of real capacitors versus frequency. Note that the capacitors behave like inductors above a few MHz [source: Cornell Dubilier].

# **B.** LC Filters

RC filters are by far the simplest and the most common type of filter found in analog circuits, however they suffer from a relatively slow roll off of the gain: while the gain or attenuation slope can be made steeper than -20 dB/decade, the transition region, or knee of the curve (the region where the gain changes from flat to a log-log slope), will always have the same shape and frequency width.

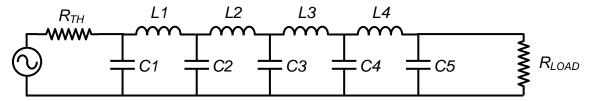

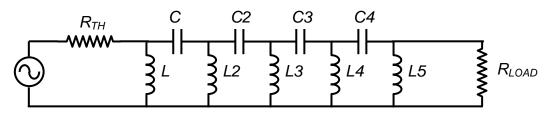

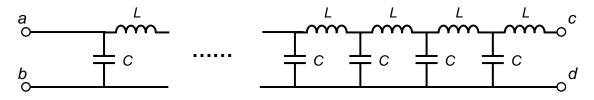

LC filters are more complex but can be engineered to produce much sharper features and steeper fall-off regions. The standard design for LC filters is an LC ladder with an un-interrupted ground line, such as in the 5<sup>th</sup> order filters shown in figure 4.7 and 4.8 below:

Figure 4.7: 5<sup>th</sup> order low-pass LC filter

Figure 4.8: 5<sup>th</sup> order high-pass LC filter

Chapter 4: Passive Analog Signal Processing

The algebra required for computing the gain and phase Bode plots for these filters is generally quite cumbersome, and a computer program (i.e. Maple or Excel) is generally useful for helping with the design. A number of web-applets can also be found on the internet for determining all the inductor and capacitor values that will produce the required filter performance.

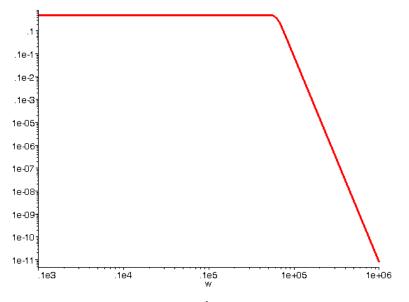

**Example 1:** 5<sup>th</sup> order Butterworth LC low-pass filter with  $f_{3dB}=10$  kHz for 50  $\Omega$  input impedance and 50  $\Omega$  output impedance. The relative amplitude of the output is shown in figure 4.9, below.

Figure 4.9: Bode plot of the gain of a 5<sup>th</sup> order Butterworth LC low-pass filter.

This Butterworth filter uses  $C1 = C5 = 0.6946 \ \mu\text{F}$ ,  $C2 = C4 = 3.0642 \ \mu\text{F}$ ,  $C3 = 4 \ \mu\text{F}$ ,  $L1 = L4 = 5 \ \text{mH}$ , and  $L2 = L3 = 9.397 \ \text{mH}$ . Butterworth filters have a very flat pass-band, and a reasonably regular phase change across the knee of the curve.

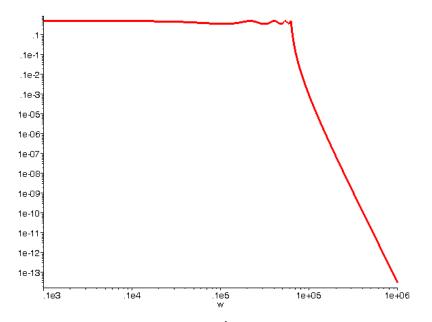

**Example 2:** 5<sup>th</sup> order Chebyshev LC low-pass filter with  $f_{3dB}=10$  kHz for 50  $\Omega$  input impedance and 50  $\Omega$  output impedance. The relative amplitude of the output is shown in figure 4.10, below.

Figure 4.10: Bode plot of the gain of a 5<sup>th</sup> order Chebyshev LC low-pass filter.

This Chebyshev filter uses  $C1 = C5 = 1.125 \ \mu\text{F}$ ,  $C2 = C4 = 1.486 \ \mu\text{F}$ ,  $C3 = 1.505 \ \mu\text{F}$ ,

L1 = L4 = 0.617 mH, and L2 = L3 = 0.646 mH. Chebyshev filters have a very sharp knee and fast cut-off, but suffer from irregular transmission in the pass-band. They also have a highly irregular phase variation at the knee of the filter.

The above Chebyshev and Butterworth filters can be scaled to another frequency or load impedance with the following rules:

$$L_{new} = \left(\frac{R_{load,new}}{R_{load,old}}\right) \left(\frac{f_{3dB,old}}{f_{3dB,new}}\right) L_{old}, \ C_{new} = \left(\frac{R_{load,old}}{R_{load,new}}\right) \left(\frac{f_{3dB,new}}{f_{3dB,old}}\right) C_{old}$$

(4.10)

# Some remarks on LC filters:

*i*. Generally, the higher the order of the LC filter, the sharper the cut-off will be, however this usually requires a trade-off in the regularity of the output phase.

*ii.* LC filters do not have resistive elements, and consequently they do not consume power, and do not load the source signal. However, the load of the input device into which the filter sends its output will load the LC filter and can shift the  $f_{3dB}$  point considerably – always remember to include the load resistor in your calculations.

*iii.* LC filters are widely used in RF circuits, where active filters do not have the bandwidth to respond to high frequencies.

*iv.* One cannot construct a filter with arbitrary gain and phase profiles. While we have treated filters in Fourier space, in the time domain filters must obey causality. In fact, one can derive Kramers-Kronig relations for filters.

# **II.** Transmission Lines

Signals are sent from one device to another, or from one part of a circuit to another with transmission lines. The quality of your transmission determines the quality of your signal, whether you are connecting one device to another or a resistor to a capacitor.

#### LC Ladder Model of a Transmission Line

A transmission line consists of two parallel conductors separated by a fixed distance d, which gives rise to an effective capacitance C per unit length. The conductors will also produce a magnetic field, which is gives the transmission line an effective inductance L per unit length. We can model the transmission line as a repeated network of series inductors and parallel capacitors, or LC ladder, as depicted in the figure below.

If the LC ladder is infinite and has an impedance  $Z_0$ , then if we add an extra LC ladder "rung", the total impedance should not change, and we obtain the following relation

$$Z_0 = (L + Z_0) / / C \Leftrightarrow Z_0 = \frac{(i\omega L + Z_0)(1/i\omega C)}{(i\omega L + Z_0) + (1/i\omega C)}$$

$$(4.11)$$

From this relation we can extract an expression for  $Z_0$ , and we obtain

$$Z_{0} = \frac{i\omega L}{2} + \sqrt{\frac{L}{C} - \frac{\omega^{2}L^{2}}{4}}$$

(4.12)

If we consider that L and C are the inductance and capacitance, respectively, of a short section  $\Delta \ell$  of transmission line, then as we take the limit  $\Delta \ell \rightarrow 0$ , we have L $\rightarrow 0$  and C $\rightarrow 0$ , but L/C $\rightarrow$  constant. In this limit the equation for  $Z_0$  becomes

$$Z_0 = \sqrt{\frac{L}{C}} \tag{4.13}$$

where L and C are the inductance and capacitance, respectively, of the transmission line, and  $Z_0$  is called the characteristic impedance of the transmission line.

It may seem surprising that a network of inductors and capacitors can have a real impedance, and consequently consume power. The explanation for this apparent paradox is that since the network is infinite, power is flowing from one LC ladder rung to the next ad infinitum, so that power is constantly moving down the transmission line, though it is

not dissipated in either the inductors or capacitors. Of course, the power is consumed at the end of the transmission line when we attach a load resistor.

The LC ladder model is a high frequency model of transmission line and does not include the wire resistance which can contribute to signal attenuation.

#### Transmission Line Impedance Matching

A transmission line with a characteristic impedance of  $Z_0$  should be terminated with a load impedance of  $Z_0$  if the transmission line is longer than 1/10 of the wavelength of the signal (recall *wavelength=c/f*, where c is the speed of light in the transmission line and *f* is the signal frequency). If the transmission line is not properly terminated, then the signal will be partially reflected back towards the source upon arrival at the load.

There are three main types of transmission lines: wires, twisted pairs, and coaxial cables. In this section we go over their performance characteristics.

# 1. Wires

Plain wires are the simplest and the cheapest transmission lines available: they include the wires you use to connect components on your breadboard and electrical grid power lines. If the wires are kept parallel, then the transmission line will provide some protection to external fields and noise at low frequencies. While wire transmission lines are simple, they should be avoided whenever possible since they are susceptible to interference and high frequency pick-up. At high frequencies a wire transmission line actually becomes an antenna (for both transmission and reception).

# 2. Twisted Pairs

A twisted pair of wires provides good protection from outside fields and noise and can transmit relatively high frequency signals without difficulty. The electro-magnetic field of a signal kept close to the wire pair. A twisted pair can transmit analog signals at up to 250 kHz (sometimes even 1 MHz) and digital signals up to 100 MHz. Twisted pairs are quite common and are used in many computer communications cable, such as RJ45 Ethernet cables which has a characteristic impedance of  $Z_0 = 100 \Omega$ . Twisted pair transmission lines are easy to make: just take two wires of equal length and twist them together!

# 3. Coaxial Cables

Coaxial cable is the best form of transmission line, short of a waveguide. In the limit of perfect conductors, signals on coaxial cables are impervious to external fields and do not radiate either. Coaxial cables can be used for frequencies up to 1 GHz. At high frequencies, a significant fraction of the transmitted energy/power is in the electric and magnetic fields that carry the signal though the cable, instead of in the potential energy of the current carrying electrons. The speed of light in a coaxial cable is usually 60-70% of

the speed of light in vacuum. The characteristic impedance of most coaxial cables used in industry and labs is  $Z_0 = 50 \ \Omega$  -- coaxial cable for cable TV is an exception, it has a characteristic impedance of 75  $\Omega$ .

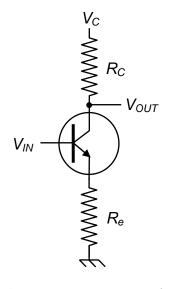

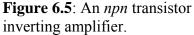

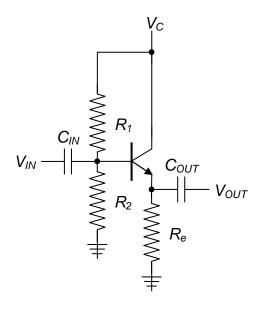

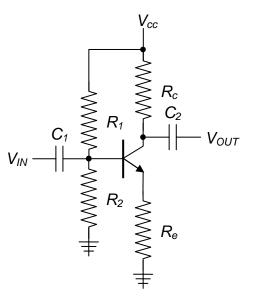

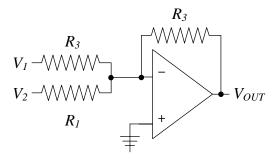

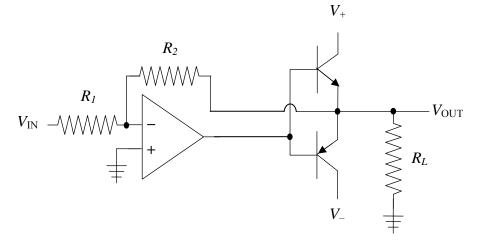

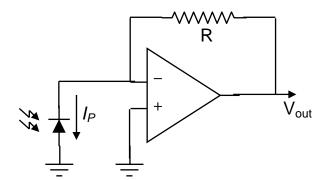

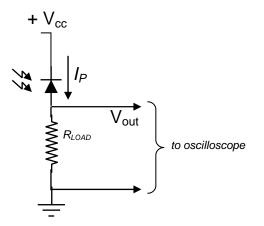

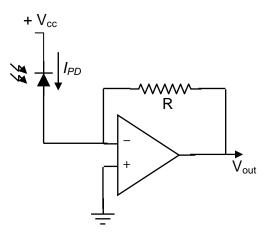

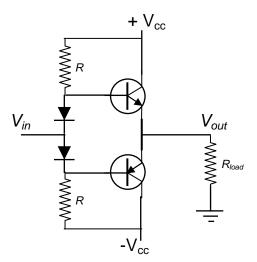

# Design Exercises: